热销产品

功率 MOSFET 基础:了解 MOSFET 与 品质因数有关的特性

简介 功率 MOSFET 已经变成了标准选择,被广泛用作低压 (<200V)开关模式电源 (SMPS)转换器应用的主开关器 件。然而,利用制造商提供的数据手册为特定电路拓扑选择 合适的器件却变得越来越困难。MOSFET 的主要选型标准是 与 MOSFET 有关的功率损耗 (与 SMPS 的总效率有关)和 MOSFET 的功耗能力 (与封装的最高结温和热性能有关)。 本应用指南重点介绍了 MOSFET 的基本特性和知识。 有几个影响 MOSFET 栅极的因素,并且在解释 MOSFET 特 性之前,有必要了解器件结构方面的基础知识。本应用指南 详细介绍了沟槽 MOSFET 结构的基本结构,进而确定了寄生 元件,定义了相关术语。还介绍了如何以及为何会产生寄生 参数。由于具有各种拓扑、开关速度、负载电流和输出电压, 所以不可能确定能够在较宽的电路条件范围内实现最佳性能 的通用 MOSFET。某些情况下以导通电阻(RDS(on))损耗为 主,而其它情况下则以瞬态电流和电压波形的开关损耗或与 器件栅极驱动有关的损耗为主。并且,还证明 (1)(2) 了输入和 输出电容也可以是主要损耗。

MOSFET 选型所用的品质因数简介

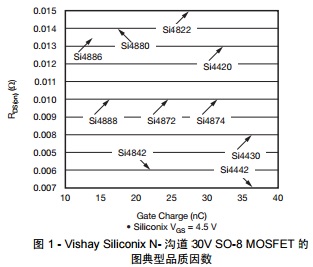

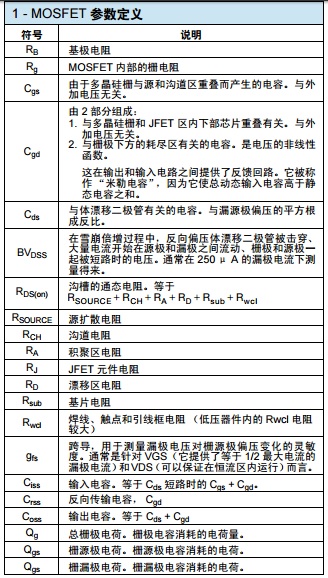

器件制造商还规定了不同静态和动态条件下的 MOSFET 参 数,让设计者难于进行同类产品对比,从而让情况变得更加 混乱。因此,唯一正确的、选择合适的 MOSFET 的方法是在 MOSFET 应用电路内比较所选器件。 有几种方法可以让设计者对比适于特定应用的 MOSFET,虽 然有时难于实现。其中一种方法就是根据品质因数来评估 MOSFET。在最简单的形式中,品质因数会在给定的 RDS(on) 下比较栅极电荷 (Qg)。乘积结果与某项器件技术有关,它 能够实现所需的 RDS(on) 或 Qg。然而,RDS(on) 越低,栅极电 荷越高。类似的器件对比方法为 “Baliga 高频品质因数” - BHFFOM(1),它假设主要开关损耗与输入电容 (Ciss)充 / 放 电 有 关。第 三 种 方 法 是 使 用 “新 高 频 品 质 因 数” - NHFFOM(2),它假设主要开关损耗因输出电容 (Coss)充 / 放电而起。后 2 种方法适于要在其中实现 MOSFET 的应用。 然而,这些方法只允许进行同类产品对比,用户无法利用它 们确定具有某一品质因数的器件是否就一定比具有另一品质 因数的不同器件好。 Vishay Siliconix 系列 30V SO-8 N- 沟道 MOSFET 样品的品 质因数 Qg x RDS(on) 如图 1 所示。例如,在某些开关应用中, Si4888DY 可能优于 Si4842DY,但是不可能利用该图 - 或者 其它采用了更复杂的品质因数的图 - 来客观地确定最适于特 定应用的器件。 MOSFET 结构 大多数 MOSFET 参数和沟槽 MOSFET 的寄生参数的一般定 义如表 1 所示。 任何功率 MOSFET 器件的基础都源于垂面 DMOS 技术。电 源产生的电流沿着表面横向流动,然后转向并沿着垂直方向 从相邻体扩散之间的表面流走,穿过外延漏区、流入基片、再 流出背面的晶圆。沿平面在多晶硅栅层下形成沟道。然而,与 沟槽结构相比,平面结构的单元密度有限,因为在超高单元 密度下, JFET 夹断效应 (1) 会增加器件导通电阻。 由于这类电气与几何限制,不仅无法保证将平面 DMOS 单元 密度进一步提高到 3000 万单元 / 平方英寸以上,而且还极有 可能降低性能。只有消除夹断效应,才能通过减少单元数量 大幅降低 MOSFET 导通电阻。

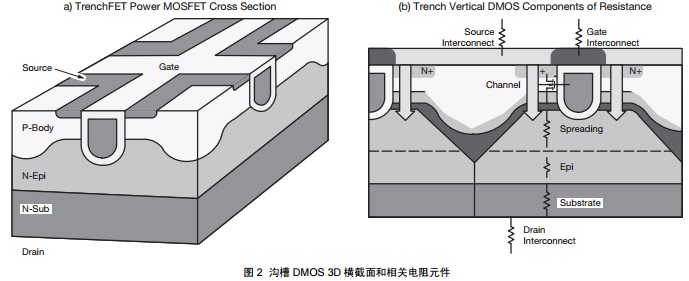

为了克服平面夹断问题, Vishay Siliconix 器件的设计者实现 了沟槽栅垂直功率 MOSFET 或 TrenchFET。不是沿表面导 电, TrenchFET 通过沿着蚀入芯片的沟槽侧壁垂直形成的沟 道导电。 沟槽 DMOS 横截面如图 2 所示。利用类似于平面 DMOS 的 封闭单元模式,沟槽形成了一个环绕硅岛的栅极。每个硅岛 都是双扩散沟道区和发生相关源极扩散的地方。 沟槽被氧化,然后用导体填充,最后被展平以形成器件栅极。 利用这项沟槽技术,可以在不产生JFET夹断效应的情况下提 高单元密度,同样可以实现高单元密度 (>2 亿单元 / 平方英 寸)。提高到该单元密度水平是很有益的,这样就可以创建一 系列能够均衡超低导通电阻、栅极特性和成本的器件。然而, 单位晶圆上晶片数量的增加(会提高成本优势)和 RDS(on) 降 低 (会提升性能)仍然是 2 大优势。 密度为 1.78 亿单元 / 平方英寸的 MOSFET 沟槽晶片的横截面 如图 3 所示。这部分穿过了区内的超高密度晶圆,展示了高 密度单元扩展。为了实现这种单元数字,重点需要放在横向 和垂直单元扩展上,这样不仅可以优化 RDS(on),还可以优化 栅极特性。 随着设计用于提高单元密度的横向扩展的发展,相关电容 (如图 3b 所示)得到了改善,从而加强了快速开关,这对于 高频操作 (>400kHz)是不可或缺的。此外,在轻电流负载 下,栅极驱动损耗成了影响总系统效率的重要因素,所以必 须考虑栅极电容。 通过改善垂直扩展,降低了电容,进而降低了 RDS(on)x Qg 值 (低于 100 (m Ω x nC))。 DMOS沟槽MOSFET的导通电阻是活动载流子必须流经的各 个区域的电阻之和 (如图 2 所示)。

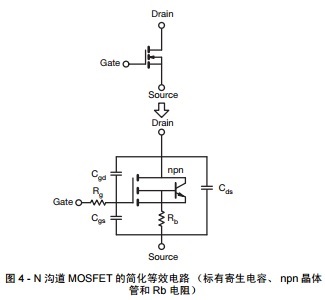

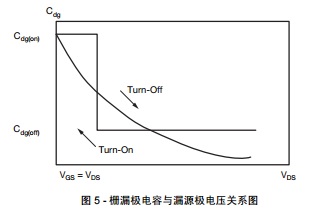

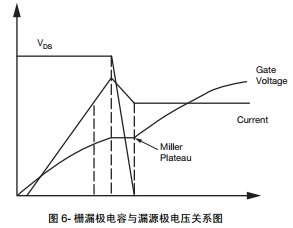

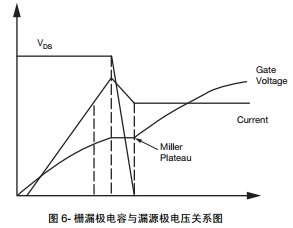

应该注意的是,对于平面 MOSFET 而言,RRDS(on) 值还包含 JFET 元件电阻。 MOSFET 的寄生电容 N-沟道MOSFET的简图如图4所示,其中三个电容,即Cgd、 Cds 和 Cgs,代表寄生电容。这些数值可以计算出输入电容、 输出电容和反向传输电容,如表 1 所述。 然而,应该注意的是,由于等效电路不光包含 1 个电阻和 3 个电容,而是要复杂得多,所以这些电容只可用于了解开关 瞬态的特性。 栅漏极电容 Cgd 和栅源极电容 Cgs 属于压敏电容,因此电容 值随施加在漏源极和器件的栅源极上的电压而变。Cgd的变化 比 Cgs 大得多,只不过是因为其上施加的电压比 Cgs 上的大 得多。Cgd 的变化 (1) 如图 5 所示,可能高达 100 倍,通常接 近于 2 个静态值。这些电容变化会影响施加在器件栅极上的 电压,从而形成米勒平台 (1)。这会在发生开关瞬态时产生断 开和接通上升与下降时间,还会 “拉平”栅极电压,如图 6 所示。

结论 本应用指南是一系列介绍在开关模式电源内实现的功率 MOSFET 的基本特性与工作性能的技术文档中的第一部。本 应用指南旨在向读者全面介绍 Vishay Siliconix MOSFETs 所 采用的器件技术。 FOM 本身不能让电源设计者选出理想器件,但却概括了器件技术和可能实现的性能。要进行可靠的主观分析,则必须修 改每个 FOM,以便包含 MOSFET 应用方面的信息。因此, 本应用指南定义了为特定应用选择合适的器件时需要考虑的 主要特性 (表 1)。

MOSFET 选型所用的品质因数简介

器件制造商还规定了不同静态和动态条件下的 MOSFET 参 数,让设计者难于进行同类产品对比,从而让情况变得更加 混乱。因此,唯一正确的、选择合适的 MOSFET 的方法是在 MOSFET 应用电路内比较所选器件。 有几种方法可以让设计者对比适于特定应用的 MOSFET,虽 然有时难于实现。其中一种方法就是根据品质因数来评估 MOSFET。在最简单的形式中,品质因数会在给定的 RDS(on) 下比较栅极电荷 (Qg)。乘积结果与某项器件技术有关,它 能够实现所需的 RDS(on) 或 Qg。然而,RDS(on) 越低,栅极电 荷越高。类似的器件对比方法为 “Baliga 高频品质因数” - BHFFOM(1),它假设主要开关损耗与输入电容 (Ciss)充 / 放 电 有 关。第 三 种 方 法 是 使 用 “新 高 频 品 质 因 数” - NHFFOM(2),它假设主要开关损耗因输出电容 (Coss)充 / 放电而起。后 2 种方法适于要在其中实现 MOSFET 的应用。 然而,这些方法只允许进行同类产品对比,用户无法利用它 们确定具有某一品质因数的器件是否就一定比具有另一品质 因数的不同器件好。 Vishay Siliconix 系列 30V SO-8 N- 沟道 MOSFET 样品的品 质因数 Qg x RDS(on) 如图 1 所示。例如,在某些开关应用中, Si4888DY 可能优于 Si4842DY,但是不可能利用该图 - 或者 其它采用了更复杂的品质因数的图 - 来客观地确定最适于特 定应用的器件。 MOSFET 结构 大多数 MOSFET 参数和沟槽 MOSFET 的寄生参数的一般定 义如表 1 所示。 任何功率 MOSFET 器件的基础都源于垂面 DMOS 技术。电 源产生的电流沿着表面横向流动,然后转向并沿着垂直方向 从相邻体扩散之间的表面流走,穿过外延漏区、流入基片、再 流出背面的晶圆。沿平面在多晶硅栅层下形成沟道。然而,与 沟槽结构相比,平面结构的单元密度有限,因为在超高单元 密度下, JFET 夹断效应 (1) 会增加器件导通电阻。 由于这类电气与几何限制,不仅无法保证将平面 DMOS 单元 密度进一步提高到 3000 万单元 / 平方英寸以上,而且还极有 可能降低性能。只有消除夹断效应,才能通过减少单元数量 大幅降低 MOSFET 导通电阻。

为了克服平面夹断问题, Vishay Siliconix 器件的设计者实现 了沟槽栅垂直功率 MOSFET 或 TrenchFET。不是沿表面导 电, TrenchFET 通过沿着蚀入芯片的沟槽侧壁垂直形成的沟 道导电。 沟槽 DMOS 横截面如图 2 所示。利用类似于平面 DMOS 的 封闭单元模式,沟槽形成了一个环绕硅岛的栅极。每个硅岛 都是双扩散沟道区和发生相关源极扩散的地方。 沟槽被氧化,然后用导体填充,最后被展平以形成器件栅极。 利用这项沟槽技术,可以在不产生JFET夹断效应的情况下提 高单元密度,同样可以实现高单元密度 (>2 亿单元 / 平方英 寸)。提高到该单元密度水平是很有益的,这样就可以创建一 系列能够均衡超低导通电阻、栅极特性和成本的器件。然而, 单位晶圆上晶片数量的增加(会提高成本优势)和 RDS(on) 降 低 (会提升性能)仍然是 2 大优势。 密度为 1.78 亿单元 / 平方英寸的 MOSFET 沟槽晶片的横截面 如图 3 所示。这部分穿过了区内的超高密度晶圆,展示了高 密度单元扩展。为了实现这种单元数字,重点需要放在横向 和垂直单元扩展上,这样不仅可以优化 RDS(on),还可以优化 栅极特性。 随着设计用于提高单元密度的横向扩展的发展,相关电容 (如图 3b 所示)得到了改善,从而加强了快速开关,这对于 高频操作 (>400kHz)是不可或缺的。此外,在轻电流负载 下,栅极驱动损耗成了影响总系统效率的重要因素,所以必 须考虑栅极电容。 通过改善垂直扩展,降低了电容,进而降低了 RDS(on)x Qg 值 (低于 100 (m Ω x nC))。 DMOS沟槽MOSFET的导通电阻是活动载流子必须流经的各 个区域的电阻之和 (如图 2 所示)。

应该注意的是,对于平面 MOSFET 而言,RRDS(on) 值还包含 JFET 元件电阻。 MOSFET 的寄生电容 N-沟道MOSFET的简图如图4所示,其中三个电容,即Cgd、 Cds 和 Cgs,代表寄生电容。这些数值可以计算出输入电容、 输出电容和反向传输电容,如表 1 所述。 然而,应该注意的是,由于等效电路不光包含 1 个电阻和 3 个电容,而是要复杂得多,所以这些电容只可用于了解开关 瞬态的特性。 栅漏极电容 Cgd 和栅源极电容 Cgs 属于压敏电容,因此电容 值随施加在漏源极和器件的栅源极上的电压而变。Cgd的变化 比 Cgs 大得多,只不过是因为其上施加的电压比 Cgs 上的大 得多。Cgd 的变化 (1) 如图 5 所示,可能高达 100 倍,通常接 近于 2 个静态值。这些电容变化会影响施加在器件栅极上的 电压,从而形成米勒平台 (1)。这会在发生开关瞬态时产生断 开和接通上升与下降时间,还会 “拉平”栅极电压,如图 6 所示。

结论 本应用指南是一系列介绍在开关模式电源内实现的功率 MOSFET 的基本特性与工作性能的技术文档中的第一部。本 应用指南旨在向读者全面介绍 Vishay Siliconix MOSFETs 所 采用的器件技术。 FOM 本身不能让电源设计者选出理想器件,但却概括了器件技术和可能实现的性能。要进行可靠的主观分析,则必须修 改每个 FOM,以便包含 MOSFET 应用方面的信息。因此, 本应用指南定义了为特定应用选择合适的器件时需要考虑的 主要特性 (表 1)。

服务热线:021-58979561

业务咨询qq:447495955

业务咨询qq:1852433657

业务咨询qq:513845646

技术支持qq:313548578

技术交流群:376450741

业务咨询:

业务咨询:

业务咨询:

技术支持:

媒体合作:

沪ICP备09068927号 igbt8.com版权所有 Copyright 2008-2018

URL:http://www.igbt8.com qq:1852433657 欢迎加入IGBT技术交流群:376450741

技术支持: IGBT应用技术网

URL:http://www.igbt8.com qq:1852433657 欢迎加入IGBT技术交流群:376450741

技术支持: IGBT应用技术网