热销产品

移相全桥ZVS PWM直流变换器元件参数设计

电路组成和工作原理

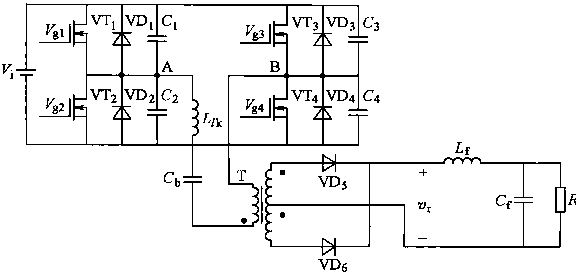

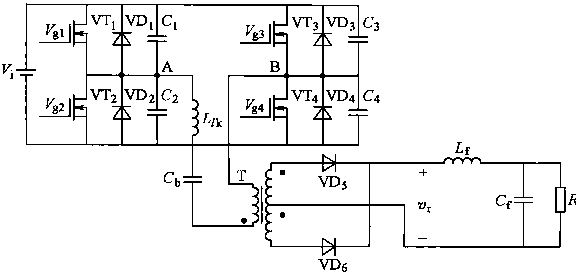

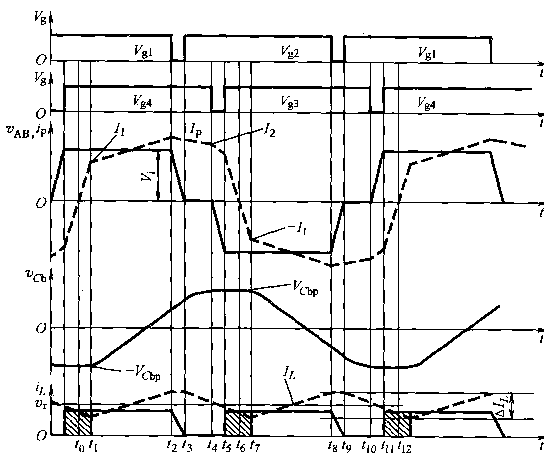

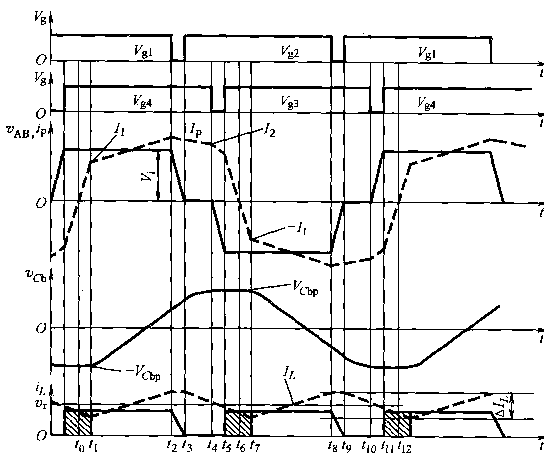

移相全桥型零电压开关(PS FB ZVS)PWM DC/DC变换器是较早出现的一种全桥软开关变换器,它是利用功率开关管的寄生电容或外接电容和变压器的漏感或一次侧串联电感作为谐振元件,而使四个开关管实现零电压开通和零电压关断(也称准零电压关断),其电路和主要工作波形分别如下图所示。文章来源:http://www.igbt8.com/bl/392.html

PS FB ZVS PWM DC/DC变换器电路

PS FB ZVS PWM DC/DC变换器的主要工作波形

主要元件参数的选择原则

(1) 隔直电容cL的选取

由前述知,全桥变换器中变压器两端承受的是正负电压,变压器磁心工作在一、三象限。但因开关管的不一致性以及驱动电路的分散性,容易使高频变压器一次侧的正负脉冲电压不对称,产生直流偏磁,若不采取措施加以抑制,长时间工作,变压器磁心会饱和,使开关管损坏。为防止变压器正、负脉冲伏秒面积不平衡,常在变压器一次侧串联一无极性的薄膜电容,隔离引起变压器直流偏磁的直流电压,从而达到抑制直流偏磁的目的。

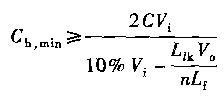

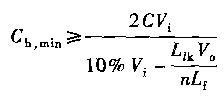

为了减小隔直电容的损耗,提高变换器的效率,隔直电容值不能太小,一般要求隔直电容电压峰值VCbp=10%Vi;同时,为了减小体积,节约成本,隔直电容值不能太大,因此需综合考虑选择Cb。

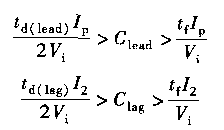

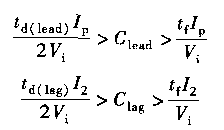

隔直电容的选择应满足:

(2)开关管并联电容的选择

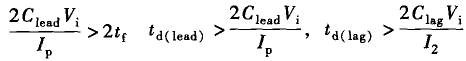

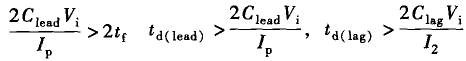

为了保证开关管实现ZVS,并联电容充、放电时间必须大于2tf(df为功率IGBT关断时间),同时,死区时间必须大于电容的充、放电时间,即

超前桥营和滞后桥臂并联电容的选择分别应满足:

(3)一次侧串联谐振电感的设计

谐振电感的选取应保证其上存储的能量能满足开关管ZVS的条件。

1)超前桥臂实现ZVS的能量条件:在VT1和VT2开、关过程中,谐振电感由输出滤波电感Lf的一次侧折算值n^2Lf和一次电感Llk串联构成。一般来说,n^2Lf值很大,电感储能很容易使电容C1、C2完成充放电状态转换。由前述知,超前臂开关管(VT1或VT2)关断时,一次电流ip在正、负方向达到其最大值Ip。同时,考虑到变压器一次绕组电容,还要一部分能量来抽走变压器一次绕组寄生电容CTR上的电荷。

2)滞后桥臂实现ZVS的能量条件:在VT3和VT4开、关过程中,二次侧整流二极管向时导通,变压器二次绕组两端电压为零,一次侧电感仅为谐振电感Llk。谐振时,Llk释放储能,使VT3、VT4并联电容完成充放电状态转换。当其一并联电容电压谐振下降到零时,相应的开关管实现ZVS。由式当Cb<Cb(crit)时,一次电流较小,Llk储能较小,因此,滞后桥臂ZVS条件需按较小的电流来考虑。

附加谐振电感的目的就是为了实现滞后臂开关管的ZVS,如前面的分析,滞后臂谐振时次级电感不能通过变压器反射到初级,为了保证滞后臂的开关管ZVS,那么谐振电感的能量必须满足下式:

LrI2p/2=( V2in*C上管)/2+( V2in*C下管)/2=V2in*Clag

即 Lr= 2* V2in*Clag /I2p

其中 Lr :谐振电感值

Vin:输入电压

Clag:滞后桥臂电容(外加电容与MOSFET结电容)

Ip:滞后桥臂关断时刻原边电流大小

计算还要考虑以下几点因素:

①、Vin应取最高输入电压值,保证任意输入电压下,滞后桥臂均能实现ZVS。

②、考虑在轻载Ipl(10%-20%负载)时刻,需要滞后桥臂仍然需要工作在ZVS状态。

③、输出电流iLf在某个值(比如2A)时刻,输出储能电感电流任然连续或处在临界点。

也就是说,输出储能电感的脉动电流等于2倍此值

即 △ iLf = 2 *2A=4A

那么 Ip=(Ipl+ △ iLf /2)/n

(4)输出储能电感设计:

移相全桥的输出储能电感其实可以看做一个单纯的BUCK电感,由于其正负半周期各工作一次,所以其工作频率等于2倍开关频率,其计算公式为:

Lf = Vo *(1-Dmin)/(4*fs* △I)

上式中的Lf是最小电感,实际取值要大于此值,以保证电流的连续性,如果需要输出电压在一定范围内连续可调的话,则Vo要取Vo(min),即

Lf = Vo(min) *(1-Dmin)/(4*fs* △I)

上式Dmin是为了便于理解,实际上移相全桥占空比是不变的,不存在最小占空比的说法:即

Dmin= Vo(min)/(Vin(max)/n-VLf-VD)

(5)主变压器设计:

首先计算出移相全桥的次级输出最低电压:

Vsec(min)=( Vo(max)+VLf+VD)/ Dsec(max)

初次级的变压器匝比为:

n=Vin(min) /Vsec(min)

选择变压器,使用Ap法:

Ap =Ae*Aw= Po*104 /(4*ƞ*fs*△B*J*Ku*)

接下来计算变压器原边匝数:

Np= Vin(min)*D(max)/(4*fs*Ae*Bmax)

那么次级绕组匝数为:

Ns= Np/n

附加谐振电感的目的就是为了实现滞后臂开关管的ZVS,如前面的分析,滞后臂谐振时次级电感不能通过变压器反射到初级,为了保证滞后臂的开关管ZVS,那么谐振电感的能量必须满足下式:

LrI2p/2=( V2in*C上管)/2+( V2in*C下管)/2=V2in*Clag

即 Lr= 2* V2in*Clag /I2p

其中 Lr :谐振电感值

Vin:输入电压

Clag:滞后桥臂电容(外加电容与MOSFET结电容)

Ip:滞后桥臂关断时刻原边电流大小

计算还要考虑以下几点因素:

①、Vin应取最高输入电压值,保证任意输入电压下,滞后桥臂均能实现ZVS。

②、考虑在轻载Ipl(10%-20%负载)时刻,需要滞后桥臂仍然需要工作在ZVS状态。

③、输出电流iLf在某个值(比如2A)时刻,输出储能电感电流任然连续或处在临界点。

也就是说,输出储能电感的脉动电流等于2倍此值

即 △ iLf = 2 *2A=4A

那么 Ip=(Ipl+ △ iLf /2)/n

(4)输出储能电感设计:

移相全桥的输出储能电感其实可以看做一个单纯的BUCK电感,由于其正负半周期各工作一次,所以其工作频率等于2倍开关频率,其计算公式为:

Lf = Vo *(1-Dmin)/(4*fs* △I)

上式中的Lf是最小电感,实际取值要大于此值,以保证电流的连续性,如果需要输出电压在一定范围内连续可调的话,则Vo要取Vo(min),即

Lf = Vo(min) *(1-Dmin)/(4*fs* △I)

上式Dmin是为了便于理解,实际上移相全桥占空比是不变的,不存在最小占空比的说法:即

Dmin= Vo(min)/(Vin(max)/n-VLf-VD)

(5)主变压器设计:

首先计算出移相全桥的次级输出最低电压:

Vsec(min)=( Vo(max)+VLf+VD)/ Dsec(max)

初次级的变压器匝比为:

n=Vin(min) /Vsec(min)

选择变压器,使用Ap法:

Ap =Ae*Aw= Po*104 /(4*ƞ*fs*△B*J*Ku*)

接下来计算变压器原边匝数:

Np= Vin(min)*D(max)/(4*fs*Ae*Bmax)

那么次级绕组匝数为:

Ns= Np/n

服务热线:021-58979561

业务咨询qq:447495955

业务咨询qq:1852433657

业务咨询qq:513845646

技术支持qq:313548578

技术交流群:376450741

业务咨询:

业务咨询:

业务咨询:

技术支持:

媒体合作:

沪ICP备09068927号 igbt8.com版权所有 Copyright 2008-2018

URL:http://www.igbt8.com qq:1852433657 欢迎加入IGBT技术交流群:376450741

技术支持: IGBT应用技术网

URL:http://www.igbt8.com qq:1852433657 欢迎加入IGBT技术交流群:376450741

技术支持: IGBT应用技术网